# Report about trusted life cycle design methodology for OSH

| Project number                               | 101070008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Project acronym                              | ORSHIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Project title                                | Open source ReSilient Hardware and software for<br>Internet of thiNgs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Start date of the project                    | 1 <sup>st</sup> October, 2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Duration                                     | 36 months                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Call                                         | HORIZON-CL3-2021-CS-01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Deliverable type                             | Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Deliverable reference number                 | CL3-2021-CS-01/ D2.1/ 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                              | CE3-2021-CS-017 D2.17 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Work package contributing to the deliverable | WP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Due date                                     | JUN 2023 – M09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Actual submission date                       | 28 <sup>th</sup> June 2023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Responsible organisation                     | SEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Editor                                       | Stefano Cristalli                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Dissemination level                          | PU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Revision                                     | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Revision                                     | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Abstract                                     | This document lays the foundation for defining and<br>modelling the concept of Trusted Life Cycle (TLC)<br>for secure, open source hardware components.<br>Specifically, a starting set of requirements for the<br>TLC is provided.<br>It also contains a novel definition of open source<br>hardware, for evaluating it qualitatively and also<br>quantitatively.<br>Another contribution is represented by the<br>evaluation of current methodologies for component<br>and vulnerability tracking, and a proposition for a<br>modern approach aimed at improving the current<br>situation. |

| Keywords                                     | Trusted Life Cycle, Secure development, Open<br>source, Hardware, Process requirements, Secure<br>processes, Secure procedures, Component<br>tracking, Bill Of Materials, Vulnerability tracking                                                                                                                                                                                                                                                                                                                                                                                             |

Funded by the European Union under grant agreement no. 101070008. Views and opinions expressed are however those of the author(s) only and do not necessarily reflect those of the European Union. Neither the European Union nor the granting authority can be held responsible for them.

### Editor

Stefano Cristalli (SEC)

#### **Contributors** (ordered according to beneficiary numbers)

Volodymyr Bezsmertnyi (NXP) Guido Bertoni, Filippo Melzani, Massimo Ratti, Stefano Cristalli, Maria Chiara Molteni, Marta Fornasier, Lorenzo Nava, Arianna Gringiani (SEC) Clarisse Ginet, Olivier Thomas (TXP) Jan Pleskac (TRPC)

#### Reviewers

Barbara Gaggl, Michael Käfinger (TEC) Daniele Antonioli (ECM) Jan Pleskac (TRPC)

#### Disclaimer

The information in this document is provided "as is", and no guarantee or warranty is given that the information is fit for any particular purpose. The content of this document reflects only the author's view – the European Commission is not responsible for any use that may be made of the information it contains. The users use the information at their sole risk and liability.

# **Executive Summary**

This document lays the foundation for defining and modelling the concept of **Trusted Life Cycle (TLC)** for secure, open source hardware components.

The first challenge that we encountered was providing a definition of *open source hardware*. Although there is extensive literature for both the worlds of "open source" and "hardware" (e.g., [Kelty 2016] [Free Software Foundation 2017], [Baker 2011]), their intersection brings new valuable context, with associated initial challenges, specific concepts, and open problems. There is enough separation within these concepts from existing literature to create a new domain of knowledge. One of such challenges, for example, is agreeing on a clear definition of what *open source hardware* means. To the best of our knowledge, this is the first work that tries to define a systematic approach for such a definition.

After a preliminary reasoning on the semantics that a definition of open source hardware should capture, and comparing it with previous attempts ([OSHWA 2023]), we present a new definition that permits the evaluation of open source hardware, both qualitatively and, for the first time, also quantitatively.

Our model distinguishes between different types of hardware *views*, based on the abstraction level of the development. Our idea is that, although grouped under the umbrella term "hardware", different developments may have different properties, and therefore deserve separate categorizations (e.g., a technology library vs. a PCB).

With a sound definition of open source hardware, we then proceed listing the requirements for the Trusted Life Cycle. These are "process" requirements about the phases which compose the development of secure open source hardware components.

For this definition task, we cannot ignore the vast literature that exists on the topic of Secure Development Life Cycles (SDLCs). Although focused more on the software domain, and usually lacking any reference to open source topics, existing models for SDLCs contain valuable and reusable knowledge also for ORSHIN's TLC.

Most of this previous knowledge on SDLCs is consolidated in IT and industry standards; therefore, we present the main relevant works, and try to summarise the commonalities.

Afterwards, starting from a baseline work from ENISA regarding good practices for security in IoT, we draft the requirements for the ORSHIN's TLC. In particular, we adapt the existing requirements to the new context of open source hardware, and we also draft new requirements that are specific for such domain. We align the definition of TLC requirements with the framework previously defined for the definition of open source hardware, in order to keep a coherent approach that has the possibility of adapting to our previously-defined hardware views.

We also consider a novel approach regarding the definition of process requirements, that is the possibility of adapting the development process according to a threat model. This allows the adaptation of a common set of requirements to specific industry use cases, possibly with dedicated personalization and extensions. Our work is harmonised with ORSHIN's Task 2.2. The content of this deliverable has been employed as a reference for developing the AttackDefense Framework (ADF) proposed by Deliverable 2.2. Specifically, the TLC was used as a reference life cycle and evaluated within the ADF case studies. Moreover, our TLC methodology is the concept at the base of the work produced in WP3, WP4, and WP5.

Finally, after having established a methodology for defining the requirements of the ORSHIN TLC, we tackle important themes related to the development of open source hardware. Specifically, we work on the definition of Hardware Bills Of Materials (HBOMs), as the focal point that has to function properly in order to allow efficient categorization of both hardware components, and of associated information that is relevant for security, such as known vulnerabilities that affect hardware components. We review existing approaches for the definition of Bills Of Materials (BOMs) in general, including relevant work done for Software Bills Of Materials (SBOMs). We challenge the Common Platform Enumeration (CPE), the industry standard for categorising hardware and software components, highlighting some problems that don't make it suitable, in our opinion, to the context of

secure open source hardware. We make a proposition for a more flexible system, starting from an extension of the Open Worldwide Application Security Project (OWASP) CycloneDX format.

We conclude the document by summarising our contribution, highlighting open problems and listing promising directions for future work.

# **Table of Content**

| Chapter 1 Ir | ntroduction                                                   | 1  |

|--------------|---------------------------------------------------------------|----|

| 1.1 Def      | inition of Open source Hardware                               | 1  |

| 1.2 Def      | inition of the Trusted Life Cycle                             | 1  |

| 1.3 Cor      | nponent and Vulnerability Tracking                            | 2  |

| 1.4 Cor      | nclusion and Next Steps                                       | 3  |

| Chapter 2 D  | efinition of Open source Hardware                             | 4  |

| 2.1 Ove      | erview                                                        | 4  |

| 2.2 Sta      | te-of-the-art                                                 | 5  |

| 2.2.1        | Licence for an Open Source Project                            | 5  |

| 2.3 Vie      | WS                                                            | 6  |

| 2.4 Pro      | perties                                                       | 8  |

| 2.4.1        | Applicability of Properties to Views                          | 10 |

| 2.4.2        | Categorization of Properties in Sets                          | 11 |

| 2.5 Hov      | v to Score Hardware Open sourceness                           | 12 |

| 2.5.1        | Properties Score                                              | 12 |

| 2.5.2        | Final Score                                                   | 14 |

| 2.6 Hov      | v to Apply our Open source Definition: Case Studies           | 16 |

| 2.6.1        | V0 - Technology Library                                       | 17 |

| 2.6.2        | V1 – CPU / IP                                                 | 18 |

| 2.6.3        | V2 - Chip / SoM                                               | 19 |

| 2.6.4        | V3 - Device                                                   | 20 |

| 2.7 Hov      | v to Score Hardware with Subcomponents                        | 21 |

| 2.7.1        | Numeric Subcomponent Scoring Example                          | 22 |

| 2.7.2        | Case Study: Raspberry Pi 4                                    | 24 |

| 2.8 Cor      | nsiderations about this Scoring System                        | 28 |

| Chapter 3 D  | Pefinition of the Trusted Life Cycle                          | 30 |

| 3.1 Ove      | erview                                                        | 30 |

| 3.2 Sta      | te-of-the-art                                                 | 31 |

| 3.3 Rev      | view of Main Cybersecurity Standards for Process Requirements | 32 |

| 3.3.1        | ENISA Good Practices for Security of IoT                      | 32 |

| 3.3.2        | ISA/IEC 62443                                                 | 34 |

| 3.3.3        | NIST SP 800-53                                                | 36 |

| 3.3.4        | ISO 27001                                                     | 37 |

| 3.3.5        | CSA Security IoT Controls Framework                           | 39 |

| 3.3.6        | ETSI EN 303 645                                               | 40 |

| 3.4 Def      | inition of the Trusted Life Cycle Phases                      | 41 |

| 3.4.1        | Threat Modelling and Risk Assessment                          | 42 |

| 3.4.2        | Design                                                        | 43 |

|              |                                                               |    |

| 3.4.3       | Implementation                                               | 43 |

|-------------|--------------------------------------------------------------|----|

| 3.4.4       | Evaluation                                                   | 43 |

| 3.4.5       | Installation                                                 | 45 |

| 3.4.6       | Maintenance                                                  | 45 |

| 3.4.7       | Retirement                                                   | 46 |

| 3.5 P       | rocess Requirements for the ORSHIN Trusted Life Cycle        | 46 |

| 3.5.1       | Selecting the Requirements                                   | 46 |

| 3.5.2       | Adapting the Requirements to ORSHIN                          | 48 |

| 3.5.3       | Hardware-specific topics                                     | 48 |

| 3.5.4       | Open source-Specific Topics                                  | 50 |

| 3.5.5       | A Proposal for the ORSHIN TLC Requirement List               | 51 |

| 3.5.6       | Applying the TLC Requirements                                | 52 |

| Chapter 4   | Component and Vulnerability Tracking                         | 56 |

| 4.1 O       | verview                                                      | 56 |

| 4.2 V       | ulnerability Management Methodology                          | 56 |

| 4.3 S       | tate-of-the-art: Component Inventory                         | 57 |

| 4.3.1       | Common Platform Enumeration (CPE)                            | 57 |

| 4.4 S       | tate-of-the-art: Vulnerability Tracking                      | 60 |

| 4.4.1       | Common Vulnerabilities and Exposures (CVE)                   | 60 |

| 4.4.2       | Common Weaknesses Enumeration (CWE)                          | 61 |

| 4.4.3       | Common Attack Pattern Enumeration and Classification (CAPEC) | 62 |

| 4.5 M       | lodern Approach for Component and Vulnerability Tracking     | 63 |

| 4.5.1       | Model for Component Tracking Definition                      | 65 |

| 4.5.2       | Practical Example                                            | 68 |

| Chapter 5   | Conclusion and Next Steps                                    | 74 |

| List of Abb | reviations                                                   | 76 |

| Bibliograph | יאר                                                          | 79 |

| Appendix A  | A - List of process requirements for the TLC                 | 83 |

# List of Figures

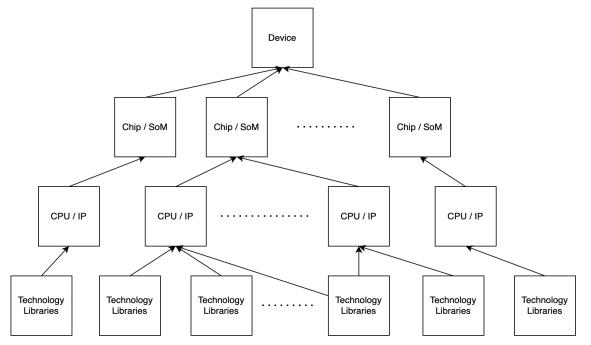

| Figure 1:An example of the hierarchical dependency among the hardware views. V0: Technolo Libraries, V1: CPU / IP, V2: Chip / SoM, V3: Device.               |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

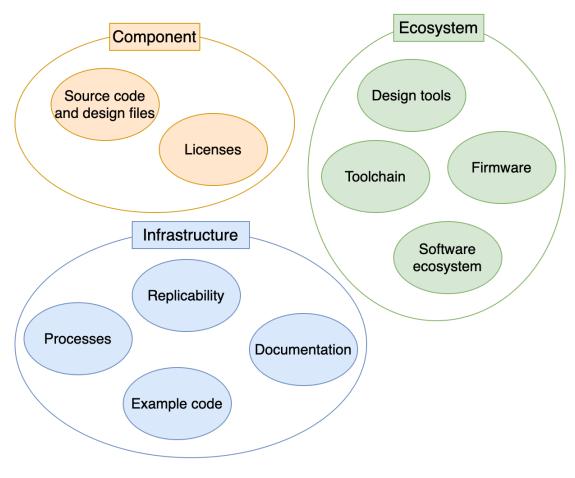

| Figure 2:The three sets in which the properties are grouped                                                                                                  | 11 |

| Figure 3: Example: computation of the final score as mean of scores in the vector                                                                            | 14 |

| Figure 4: Example: computation of the final score as mean of means of scores in the groups                                                                   | 15 |

| Figure 5: Tables for the final score computation in sheet Evaluation view 0                                                                                  | 16 |

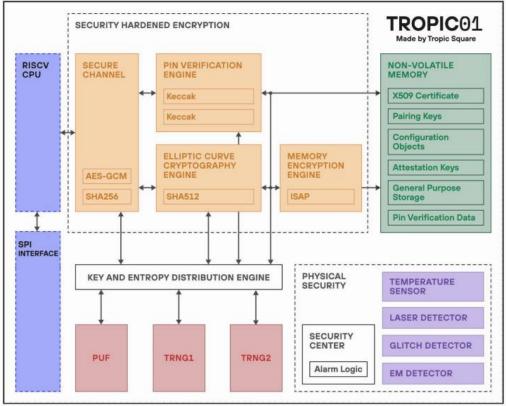

| Figure 6: TROPIC01 schematic.                                                                                                                                | 19 |

| Figure 7: Tables for the computation of the score of a component considering also the score subcomponents; one Table is for method 1 and one is for method 2 |    |

| Figure 8: Raspberry Pi 4 [Raspberry Products].                                                                                                               | 24 |

| Figure 9: Scoring Raspberry Pi4 considering the subcomponent BCM2711                                                                                         | 25 |

| Figure 10: Apalis IMX6 [Toradex Apalis]                                                                                                                      | 26 |

| Figure 11: Scoring Toradex Apalis considering the subcomponent IMX6                                                                                          | 27 |

| Figure 12: USB Armory Mk II [USB Armory Mk II]                                                                                                               | 27 |

| Figure 13: Scoring USB Armory considering the subcomponent IMX6                                                                                              | 28 |

| Figure 14: SDLC phases defined in ENISA Good Practices for Security of IoT                                                                                   | 33 |

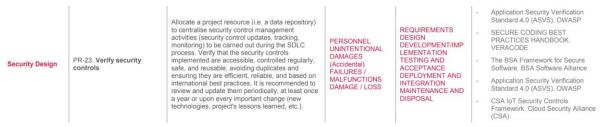

| Figure 15: An example of process security requirement defined in ENISA Good Practices for Secur of IoT.                                                      |    |

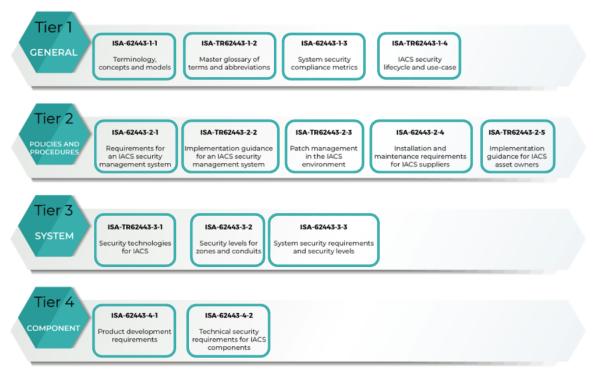

| Figure 16: The document structure of ISA/IEC 62443.                                                                                                          | 35 |

| Figure 17: NIST SP 800-53 security and privacy control families.                                                                                             | 37 |

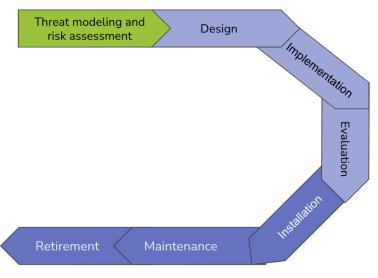

| Figure 18: Seven phases of the Trusted Life Cycle.                                                                                                           | 42 |

| Figure 19: Comparison of CVE, CWE and CAPEC. Copyright © The MITRE Corporation                                                                               |    |

| Figure 20: NXP MIMXRT685, source [NXP RT600 Datasheet].                                                                                                      | 69 |

| Figure 21: U-blox LARA-R6001 simplified block diagram, source [U-blox LARA-R6 Datasheet]                                                                     | 69 |

| Figure 22: The BOM of the ORSHIN device example                                                                                                              | 70 |

# List of Tables

| Table 1: Hardware views                                                                   | 8     |

|-------------------------------------------------------------------------------------------|-------|

| Table 2: View properties                                                                  | 9     |

| Table 3: Descriptions of the scores for each property                                     | 12    |

| Table 4: Scoring for the Technology Library UMC with the second method                    | 17    |

| Table 5: Scoring for Open Titan with the second method                                    | 18    |

| Table 6: Scoring for TROPIC01 with second method.                                         | 20    |

| Table 7: Scoring for Trezor with the second method.                                       | 21    |

| Table 8: Numerical example of how to score a component taking into account its subcompone | ents. |

|                                                                                           | 23    |

| Table 9: Analysis of the Raspberry PI4                                                    | 24    |

| Table 10: Analysis of the Broadcom BCM2711                                                | 25    |

| Table 11: Analysis of the Toradex Apalis IMX6                                             | 26    |

| Table 12: Analysis of the NXP IMX6.                                                       | 27    |

| Table 13: Analysis of the USB Armory Mk II                                                | 28    |

| Table 14: ISA/IEC 62443-4-2 Security Levels.                                              | 36    |

| Table 15: The 7 clauses from ISO 27001                                                    | 38    |

# Chapter 1 Introduction

In this document we report part of the research of WP2, particularly focusing on the work related to the ORSHIN Trusted Life Cycle methodology (Task 2.1). In this project we discuss electronic hardware, and then all the reasoning and examples in this document are focused on that area.

The concept of Secure Development Life Cycle (SDLC) is consolidated and extensively applied in the IT world, with recent applications also touching the Internet of Things (IoT) and Industrial Automation Control Systems (IACS) contexts. However, even the most recent embedded-oriented SDLC variations are heavily lacking when considering the topics of hardware development, and open source.

These topics, central to the ORSHIN project, guide the definition of the Trusted Life Cycle (TLC). TLC is a methodology which aims at providing developers and maintainers of the open source community with practical help for exploring and expanding the cybersecurity dimension of their projects. This methodology focuses mainly on the embedded/IoT/IIoT projects which make partial or total use of open source hardware.

This document is divided into the chapters described in the following Sections.

# **1.1 Definition of Open source Hardware**

Chapter 2 is dedicated to the definition of "open source hardware". Despite being extensively used, this terminology does not yet have a universally accepted definition, so we tackle the challenge of formalising a possible one.

We explore the context of hardware, differentiating developments into *views* based on their level of abstraction.

First, we study properties of hardware developments that influence their *effective* open source status.

Second, we provide qualitative definitions for different levels of open source hardware based on such properties, and we also study the application of properties to the different hardware views. Then, we define a score to compare open source hardware products, aiming at capturing relevant detail while maintaining simplicity of use.

We start by defining our scoring system for components based on the evaluation of single properties, and afterwards we provide a way for calculating the composite score of a device, taking into account the score of its subcomponents.

Finally, we evaluate our novel approach on real-world examples of both open source and non-open source hardware, such as Raspberry Pi4, USB Armory and more.

# **1.2 Definition of the Trusted Life Cycle**

Chapter 3 provides a definition of the Trusted Life Cycle phases, and its requirements, which are the central contributions of this deliverable.

We start by reviewing previous work, which is represented by the different frameworks in the literature for the definition and application of Secure Development Life Cycles (SDLCs). In particular, we focused on sets of practices and requirements that allow developers and system integrators to build secure products and systems in a reliable and repeatable fashion. The beginning of the work on such methodologies dates back to the early 2000s, and it has a good level of maturity in its primary field of application, i.e. software development with IT infrastructure; on the other hand, newer context such as Internet of Things and Industrial Automation and Control Systems have only seen recent effort for porting the practices of SDLCs, and have therefore a lower level of maturity. In particular, hardware development is typically faced by SDLC at a high level of abstraction, without

considering the peculiarities of the hardware industry (e.g., differences while building an IT and IoT processors).

Similarly, open source is seldom mentioned by SDLC methodologies, if at all. Concerns in this direction primarily focus on the security of 3rd-party software libraries, and not much more.

Within the ORSHIN project, both hardware development and open source are central topics, and we propose a methodology that adequately addresses the definition of security requirements for them. We review the most relevant international standards and guidance documents which provide process-oriented security requirements, showing different perspectives to the definition of requirements and best practices.

We select a source that in our opinion represents the best starting point for defining a development life cycle oriented to hardware and open source, due to its starting focus on the IoT world. We perform a selection of requirements, filtering out ones that are not suitable for the properties we want for the ORSHIN Trusted Life Cycle, then we adapt their content to fully adhere to the ORSHIN context.

We draft new requirements specifically for the topics of hardware design and open source, then we provide our finalised proposal with the full list of requirements for the ORSHIN Trusted Life Cycle. Finally, we discuss methodology for the application of requirements.

# **1.3 Component and Vulnerability Tracking**

Chapter 4 faces the important topic of component and vulnerability tracking, which is a fundamental part of the *maintenance* phase of the ORSHIN Trusted Life Cycle.

In order to perform an effective monitoring of the security of developments, it is essential that their composition is known in detail.

This necessity is met by compiling the Bill Of Materials (BOM) for a component, be it software (Software Bill Of Materials - SBOM), hardware (Hardware Bill Of Materials - HBOM) or a combination of the two.

The associated requirement for effective vulnerability management is the ability to gain knowledge about recent vulnerabilities that get published in global databases about products that one wishes to monitor, or about any of their subcomponents.

For this reason, there is a rich vulnerability tracking ecosystem, including:

- Identified instances of vulnerabilities (with the Common Vulnerabilities and Exposures framework - CVE);

- Common weakness that affect various aspects of the design and implementation of systems (with the Common Weakness Enumeration framework - CWE);

- Attack patterns that allow attackers to discover vulnerabilities starting from common weaknesses (with the Common Attack Pattern Enumeration and Classification framework CAPEC).

We review the state-of-the-art for both this vulnerability-tracking ecosystem, and for its componenttracking framework counterpart, that is Common Platform Enumeration - CPE, which is currently predominantly used for referring to components and products that have been associated with some vulnerability.

We explain how the current limitations of the above systems fail at providing a lightweight and open approach for everyone to use to compile efficient BOMs with rich public information about components, and how the situation could significantly improve by leveraging a related framework from OWASP called CycloneDX.

After declaring the properties that we envision for a modern component and vulnerability tracking system, we see with a practical example how CycloneDX allows to meet most of them. We provide an extension to the format allowing modelling additional details that are relevant for the context of ORSHIN as a consequence of our research (for example, the score for open source hardware). Then, we outline the next steps that would be necessary for global adoption of our framework for satisfying the remaining requirements, which are not format-dependent. For instance, we state that a global public database would be necessary for actual adoption of a new component-

tracking system, and that participation from the community would be required at multiple levels, from manufacturers to individual researchers and enthusiasts.

# 1.4 Conclusion and Next Steps

We review the conclusions of our research in Chapter 5, and outline the next steps to continue research in promising directions.

# Chapter 2 Definition of Open source Hardware

# 2.1 Overview

The object of our work is the so-called *open source hardware*. The initial question we need to answer is: which are the guidelines to define when a hardware device is open source. For example, how can we define an open source product using a closed-design microcontroller or an open source HDL distributed with proprietary toolchain? Is it open source or not?

A starting point for giving a complete definition is the description given by the Open Source Hardware Association (OSHWA) website [OSHWA 2023]. In the introduction it is stated the following:

"Open Source Hardware (OSHW) is a term for tangible artifacts — machines, devices, or other physical things — whose design has been released to the public in such a way that anyone can make, modify, distribute, and use those things."

OSHWA considers a hardware device to be open source if it complies with the following criteria:

- The *documentation* must be provided with the device, and it must be in an open format. In particular, the documentation must include design files, and must allow their modification and distribution.

- The *software* necessary for the hardware under investigation has to be released under an open source licence. It is also desirable to have well documented interfaces, such that it will be easy to write an open source software that allows the device to operate properly and fulfil its functions.

- *Modifications* and *derived works* must be allowed, and they have to be distributed under the same term as the licence of the original work.

- *The redistribution* of the hardware needs to be for free, and it should be possible to sell or give away the project documentation.

- The Licence must not be specific to a product and it must *not restrict* other hardware or software. If a part of the product is used or distributed, it has to follow the term of the licence granted for the original work.

- The Licence must not discriminate against persons or groups, and it must not restrict anyone from making use of the work in a specific field of endeavour.

In our opinion, this description and other state-of-the-art notions and definitions (see Section 2.2 - State-of-the-art) in this context are not sufficient to provide a thorough vision. We believe that for the aim of the ORSHIN project and for practical applicability in industry, they can be a good starting point, but they also need to be extended. In this direction, we invested our first efforts in trying to provide an exhaustive and deep definition that we present in the following Sections.

To reach the goal of a complete definition, we propose a categorization of hardware components in sets that we call views (Section 2.3 Views). Once placed in a view, each component is evaluated according to different properties (Section 2.4 - Properties) which express its open sourceness under different perspectives. For any hardware, this evaluation produces a vector of scores (Section 2.5 - How to Score Hardware Open sourceness) which is then combined to reveal how much the hardware component is open source. Some examples of these evaluations are in Section 2.6 - How to Apply our Open source Definition: Case Studies, and the evaluation computed considering also the subcomponents is presented in Section 2.7 - How to Score Hardware with Subcomponents.

# 2.2 State-of-the-art

The definition of open source was born in the software context. The term open source does not simply mean that the source code is freely accessible, but also that it should follow some criteria [Open Source Initiative][Debian Social Contract 2023]. The highlighted criteria are very similar to those reported in the OSHWA website; this is because OSWHA selected the criteria for defining open source hardware by retracing and elaborating on the steps established in previous years for software.

On the Debian Organization website [Available: <u>https://opensource.org/osd/</u>.], the Debian Free Software Guidelines (DFSG) are listed in the following points.

- 1. *Free Redistribution*. The licence of a Debian component may not restrict any party from selling or giving away the software. The licence may not require a royalty or other fee for such sale.

- 2. *Source Code*. The program must include the source code, and the distribution of the source code as well as the compiled form must be allowed.

- 3. *Derived Works*. The licence must allow modifications and derived works, at which are applied the same terms as the original software.

- 4. Integrity of The Author's Source Code. This point is a compromise in the context of modification of the files. Indeed, the licence may require derived works to carry a different name or version number from the original software, in such a way to preserve the integrity of the original source code.

- 5. No Discrimination Against Persons or Groups.

- 6. No Discrimination Against Fields of Endeavour.

- 7. Distribution of Licence. The rights attached to the program must apply to all to whom the program is redistributed.

- 8. *Licence Must Not Be Specific to Debian*. The rights attached to the program must not depend on the fact that the program is part of a Debian system.

- 9. *Licence Must Not Contaminate Other Software*. The licence must not place restrictions on other software that is distributed along with the licensed software.

One of the first software open source projects is the GNU Operating System, supported by the Free Software Foundation [GNU 2021]. It was launched by Richard Stallman in 1983, with the goal of offering a Unix-compatible system that would provide completely free software. GNU packages include user-oriented applications, utilities, tools, libraries, as well as games, namely all the programs that an operating system can offer to the users.

After a first spread in the context of software, the definition of open source took hold also for hardware. In this scenario, the Open Source Hardware Association [OSHWA 2023] was born, with the aim of fostering technological knowledge and encouraging research that is accessible, collaborative and respectful of user freedom. OSHWA organises the annual Open Hardware Summit and maintains the Open Source Hardware certification [OSHWA CERT], which allows the community to quickly identify and represent hardware that complies with the community definition of open source hardware.

### 2.2.1 Licence for an Open Source Project

In choosing a licence, one should first decide whether or not he wants to require people to keep the derivatives of his designs open source. If so, he should use a *copyleft licence*; if not, he could choose a *permissive licence* [OSHWA 2023]. *Copyleft* (or viral) *licences* require derivatives to be licensed

under the same terms; on the other hand, *permissive licences* allow other people to make modifications without needing to release the derivative product as open source hardware. A designer of open source software/hardware must allow modification and commercial re-use of a design, so he should not use licences with a no-derivatives or non-commercial clause.

Some examples of licences used for open source projects are listed below.

- CERN OSH [CERN OSH 2023]: the current version of this licence is version 2, that comes with three variants, CERN-OHL-S (strongly reciprocal), CERN-OHL-W (weakly copyleft) and CERN-OHL-P (permissive). For a deeper understanding, see the document [CERN OHL 2020].

- MIT [MIT LICENCE].

- Apache2.0 [APACHE LICENCE 2023].

- GNU General Public Licence [GPL 2022].

- Creative Commons Licences [CCLICENCES].

### 2.3 Views

In this Section, we propose a categorization of hardware based on *views*.

In the ORSHIN project we discuss electronic hardware, and then all the reasoning and examples in this document are focused on that area. When talking about hardware, we can refer to many different layers, from the technology libraries used for the synthesis of circuits, to the final device, which can include multiple chips. In particular, each hardware component has a specific purpose and contributes to the overall functioning of the device.

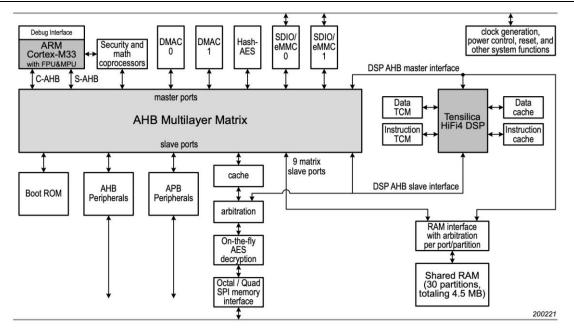

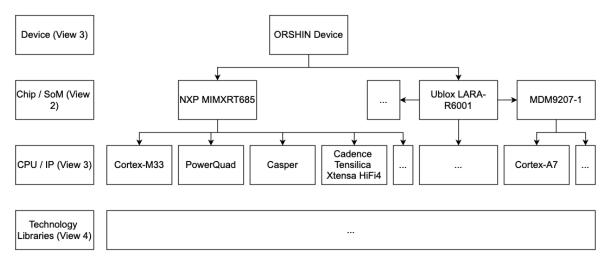

The first step toward our definition of open source hardware is the description of these different hardware layers, which we call *views* (Figure 1). Views define different types of hardware components and we identified four of them; the most basic one is the lowest view (V0), i.e. the *technology library*, which is necessary for the synthesis of any hardware component. Starting from that, we have identified other three views, until reaching the most complex hardware level, i.e., the complete *device* (V3).

Figure 1:An example of the hierarchical dependency among the hardware views. V0: Technology Libraries, V1: CPU / IP, V2: Chip / SoM, V3: Device.

Each view is described hereafter in detail.

- A **technology library**, also known as a tech library, is a collection of resources, materials, and information related to the building of hardware components. It serves as a repository of knowledge, providing access to a wide range of technological resources. The silicon manufacturers can benefit from technology libraries by accessing resources created by others, keep them updated, and provide insights into best practices and methodologies.

- A **CPU** (Central Processing Unit) is the component of a device responsible for executing instructions and performing calculations. It includes the control unit, arithmetic logic unit, registers, and cache. With the term **IP** (Intellectual Property, i.e., memories, reusable unit of logic, cryptographic accelerator, cell, or integrated circuit layout design) we denote all the other components that are not the CPU and collaborate to the functioning of the final device.

- A **chip** is a physical integrated circuit that is used in electronic devices. It is responsible for the processing, storage, and control of electrical signals within a device. Chip is a hardware component that can be buyed on the market. A **System on Module** (SoM), is a small, self-contained computing module that integrates essential components of a system onto a single board. It is designed to provide a ready-made solution for embedded system development, reducing the time, cost, and complexity of designing a custom hardware solution. A typical System on Module can consist of the following components: processor, memory, I/O interfaces, power management, and connectors.

- A **device** is a physical object that is designed and used to perform specific functions or tasks, and often requires power or energy input to operate. Devices rely on electronic circuits and components to function. For example, they contribute to communication (e.g., smartphones), productivity (e.g., laptops), entertainment (e.g., smart TV), and healthcare (e.g. wearable fitness tracker).

In Table 1 we report the identified views; each view can be linked to one or more referents, i.e. who works and deals with hardware in the correspondent view. This means that, for example, a silicon manufacturer will be interested in components that are grouped in views 0 and 1, while view 2 is related to component integrators. We identify four possible referents:

- Silicon manufacturer: company that produces silicon chips. In some cases the chip maker is an Integrated Design Manufacturer (IDM) in other cases is a pure foundry. In the latter case the foundry is producing chips for customers, a typical example is TSMC, while in the case of IDM the company design the chip itself (decide which type of CPUs, interconnection and IPs are integrated in the silicon chip)

- **Chip designer:** It can be a company, an IDM or a fabless (a company without a silicon fab) or an individual that wants to design a chip. The designer decides what should be integrated in the chip and interacts with foundry in order to deliver a set of files for the production.

- **Component integrator**: company or entity that specialises in integrating different electronic components and subsystems into a cohesive and functional system. They play a crucial role in the development and manufacturing of complex electronic products by assembling and integrating various components sourced from different manufacturers. The roles of a component integrator involve: component selection, system design and layout, component procurement, assembly and integration, testing and quality assurance, and documentation and support. We include in the category of component integrator the case of companies or individuals that delivers a final product.

- **Final user**: person or company that is placed at the end of the production-distribution-usage chain. In other words, the final recipient of the object or service that is produced which benefits from its usage.

| View                    | Referent                                                          | Description                                                                                                                                                                                                                              |  |  |  |

|-------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V0 - Technology Library | Silicon manufacturer                                              | Libraries containing the blocks to build the fundamental bases for a hardware component.                                                                                                                                                 |  |  |  |

| V1 - CPU / IP           | Silicon manufacturer or chip designer                             | The central processing unit and all<br>the subcomponents (Intellectual<br>Property) that are used to build the<br>next view.                                                                                                             |  |  |  |

| V2 - Chip / SoM         | Silicon manufacturer, Chip<br>designer or<br>Component integrator | Integrated circuit that combines<br>multiple electronic components and<br>functionalities into a single chip; the<br>subcomponents come from the<br>previous view. It is an item you can<br>buy ready made, directly from the<br>market. |  |  |  |

| V3 - Device             | Component integrator or<br>Final user                             | The hardware into the hands of the final user, which is designed and used to perform a specific function or task, and which is the final composition of parts from lower views.                                                          |  |  |  |

Table 1: Hardware views.

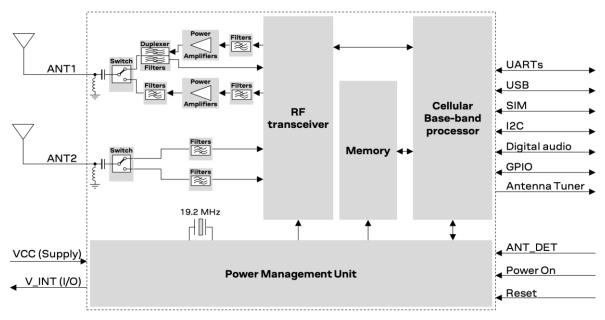

In order to model the interdependencies and connections among the components of each of the views, the most straightforward approach is to use a hierarchical topology. Indeed, a device (V3) can be composed of multiple chips and SoMs (V2), and the latter of multiple CPUs and IPs (V1), which are, in turn, based on the technology libraries (V0). A representation of such dependencies is illustrated in Figure 1. Nevertheless, in Chapter 4 - Component and Vulnerability Tracking we will discuss that these dependencies are not always hierarchical, since there are hardware components that are built with subcomponents belonging to the same view. This is, for example, the case of the u-blox cellular module LARA-R6001, which is a view-2 chip containing view-2 subcomponents (see Section 4.5.2 - Practical Example). Anyway, this interdependence of components inside the same view does not affect the considerations made in this Chapter.

# 2.4 Properties

To understand if a hardware component is open source, we have identified a list of properties to be analysed and scored. Not all of them can be applied to each view, but we tried to make them as homogeneous as possible. Moreover, we tried to be exhaustive, listing all the properties that we considered relevant in a hardware for the definition of how much it is open source.

For each component in the views, we propose the list of properties and descriptions that are in Table 2.

Table 2: View properties.

| Property                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0 – Source code and design files | The source code and design files used for building the component.<br>The source code is a collection of instructions or statements written<br>in a programming language that make up the functionalities of the<br>component. Design files serve as a blueprint or reference for<br>implementing the intended design.                                                                                                                                                                                                                                |

| P1 - Licences                     | Which kind of licence is provided. A licence, in the context of software/hardware and IP, is a legal agreement that outlines the terms and conditions under which a person or organisation is permitted to use, distribute, modify, or sell a particular software or intellectual property. Licences help protect the rights of the hardware or intellectual property creators, while providing clear guidelines for users regarding their rights and responsibilities.                                                                              |

| P2 - Design tools                 | Visual design tools (e.g., STM32CubeIDE IOC file), and other tools to support design. Design tools are software applications or platforms that assist designers in creating, editing, and managing the design elements of the hardware.                                                                                                                                                                                                                                                                                                              |

| P3 – Toolchain                    | Any software tool that processes design files and/or source code and<br>produces artefacts that are necessary for production (e.g., compiler,<br>linker, synthesis tool). A toolchain refers to a set of software tools<br>that are used together in a specific sequence. It consists of various<br>tools that perform different tasks during the development process.<br>Each tool in the toolchain typically takes the output of the previous<br>tool as its input and produces output that can be used by the<br>subsequent tool.                 |

| P4 – Software ecosystem           | A software ecosystem refers to a collection of software applications, tools, frameworks, libraries, Software Development Kits and platforms that are interconnected and interact with each other to support software development, deployment, and usage. It represents the environment in which software operates and the various components that enable its functioning. A software ecosystem typically includes: operating systems, programming languages, integrated development environments, libraries and frameworks, cloud platforms, etc.    |

| P5 - Firmware                     | The firmware running on the component and distributed with the product. Firmware refers to a type of software that is embedded within electronic devices and provides low-level control and functionality. It is a specific type of software that is stored in non-volatile memory, such as ROM (Read-Only Memory) or flash memory, and is responsible for controlling the hardware of a device. Since it is strictly related to the hardware component, firmware has to be considered in our scoring method.                                        |

| P6 - Processes                    | Any "DevSecOps"-related aspect for which the manufacturer<br>can/has to provide evidence of in order to guarantee environmental<br>security. Processes include all the activities during the hardware<br>development that integrate security practices and considerations into<br>every stage. Generally, the manufacturer emphasises collaboration<br>and shared responsibility among development, security, and<br>operations teams to ensure that security measures are implemented<br>from the beginning of the development process. Examples of |

| Property           | Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                    | processes are: security of the private key for signing update images<br>or assurance of having done security testing.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| P7 - Replicability | Whether the hardware can be easily/completely replicated starting<br>from the open source information or not. Some key aspects and<br>considerations related to replicability are: methodological<br>transparency, data availability, independent verification, sample size<br>and statistical power, replication studies, methodological rigour and<br>standardisation.                                              |  |  |  |  |  |

| P8 - Documentation | Documentation that describes the design, functionality, specifications, assembly, operation, and maintenance of hardware components or systems. Comprehensive and accurate documentation is crucial to have for various reasons, including facilitating effective communication, ensuring consistency, aiding troubleshooting and repairs, supporting future development, and complying with regulatory requirements. |  |  |  |  |  |

| P9 – Code examples | Examples that can be found in the documentation and/or online.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

The presented list of properties is *extensible* according to the hardware component under analysis. More details on this argument can be found in Section 2.8 - Considerations about this Scoring System.

### 2.4.1 Applicability of Properties to Views

Depending on the view that is taken into consideration, it may be not possible to apply a specific property to the hardware component under analysis. For example, taking into consideration the low level view, V0, it is clear that the firmware property cannot be applied. V0 represents the technology libraries, which are used to build the CPUs and IPs (V1); the elements in V0 are not capable of running firmwares. According to the design of the components included in the V0, the "firmware" property is not significant and should not be included into the analysis.

Moreover, for some views, the meaning of the properties may vary with respect to the others. For instance, the software ecosystem is completely different between V0 and V3. In general, the tools and the programming languages required to design or use components from the two views are not easily comparable in terms of functionalities, requirements, and licences. For instance, designing and using components in V0 may involve working with specific EDA designer tools and focusing on hardware-level implementation. In contrast, in V3, the focus shifts to higher-level software development, where more programming languages and frameworks may be available and a different approach is used overall (e.g.: Linux and its utilities).

Furthermore, functionalities and capabilities associated with components can differ significantly across the different views. The components of V0 may be limited to specific and basic operations (such as elementary arithmetic operations), while components of V3 may implement complex functionality (such as structured communication protocols). Thus, applying the properties to these different views is not a trivial task; and differences of a similar nature can be also observed between intermediate views. To overcome this challenge, evaluators must carefully consider the specific context, objectives, and requirements of each view when assessing the properties.

Because of the structure of View 0, our scoring template does not include the following three properties for this view:

- Software ecosystem;

- Firmware;

- Processes.

This choice derives from the previous observations and from the required level of expertise to coherently apply the scoring of such properties in the said context.

#### 2.4.2 Categorization of Properties in Sets

The properties listed in the previous Paragraph can be divided in sets, according to their sphere of belonging. Indeed, we identify three sets (Figure 2), that we list below.

- **Component**: in this set are grouped the properties related to the hardware component itself. The properties are:

- P0 Source code and design files

- P1 Licences

- **Ecosystem**: all the properties that are related to tools and software running on the hardware. In this set, the grouped properties are:

- P2 Design tools

- P3 Toolchain

- P4 Software ecosystem

- P5 Firmware

- Infrastructure: those properties that are related to a particular aspect of the component, that is not directly linked to the hardware or the running software. These properties are:

- P6 Processes

- P7 Replicability

- P8 Documentation

- P9 Code examples

### 2.5 How to Score Hardware Open sourceness

Following the structure of views and properties described in the previous Sections, it is clear that it is not possible to declare a hardware as entirely open source or closed-source. Therefore, our idea is to associate to a hardware component a view, and then compile for it a vector of scores, one score for each property. The property score ranges from 0 to 3, where 0 means that the property reflects the behaviour and features of closed-source hardware, and 3 of open source hardware. Hence, the higher the score the more open is the hardware component.

#### 2.5.1 *Properties Score*

In Table 3 we report how we score the ten properties that we have defined in Section 2.4 - Properties; for each property, we give a description of what it means scoring that property with levels from 0 to 3.

| Property                          | Scores                                                                                                                                                                                                                                                               |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P0 – Source code and design files | 0- The source code and design files are closed-source, and not documented at all.                                                                                                                                                                                    |  |  |

|                                   | 1 – The source code is poorly documented and the design files are not open source (or not completely).                                                                                                                                                               |  |  |

|                                   | 2 – The source code is well documented, but not sufficiently complete to be considered straightforward to write open source software that allows the device to operate properly and fulfil its essential functions. The design files are not completely open source. |  |  |

|                                   | 3- The source code is sufficiently documented such that it could reasonably be considered straightforward to write open source software that allows the device to operate properly and fulfil its essential functions. The design files are completely open source.  |  |  |

| P1 - Licences                     | 0 – The licence does not allow any modification or derived work. The licence restricts the parties from selling or giving away the project documentation.                                                                                                            |  |  |

|                                   | 1 – The licence imposes some important restrictions.                                                                                                                                                                                                                 |  |  |

|                                   | 2 – The licence imposes few small and irrelevant restrictions.                                                                                                                                                                                                       |  |  |

|                                   | 3 – The licence shall allow modifications and derived works, without commercial restriction. The licence shall not restrict any party from selling or giving away the project documentation.                                                                         |  |  |

| P2 - Design tools                 | 0 – The most commonly used design tools are proprietary, and are not made available to the public.                                                                                                                                                                   |  |  |

|                                   | 1 – The most commonly used design tools are proprietary, and available to the public as paid software.                                                                                                                                                               |  |  |

|                                   | 2 – The most commonly used design tools for the target platform are available under NDA or, in general, with licences that regulate their use. They are not open source.                                                                                             |  |  |

|                                   | 3 – The most commonly used design tools for the target platform are available online without restriction and are open source.                                                                                                                                        |  |  |

| P3 - Toolchain                    | 0 – The toolchain is proprietary, and it is not made available to the public.                                                                                                                                                                                        |  |  |

|                                   | 1 – The toolchain is released only under NDA or in general with licences that strictly regulate its use.                                                                                                                                                             |  |  |

Table 3: Descriptions of the scores for each property.

rshin

| Property                | Scores                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | 2 – The toolchain is freely available online, however parts of it are not released under an open source licence.                                                                                                                                                                                                                                                                 |

|                         | 3 – The toolchain for the target platform is available online without restriction and is completely open source.                                                                                                                                                                                                                                                                 |

| P4 – Software ecosystem | 0-No additional libraries / SDK to interact with the product are provided, and it is not possible to recover them.                                                                                                                                                                                                                                                               |

|                         | 1 – Additional libraries / SDK to interact with the product can be obtained by paying or signing an NDA.                                                                                                                                                                                                                                                                         |

|                         | 2 – Additional libraries / SDK to interact with the product are available with minor restrictions.                                                                                                                                                                                                                                                                               |

|                         | 3 – Additional libraries / SDK to interact with the product are provided together with the product or are available online without restrictions, and they are open source.                                                                                                                                                                                                       |

| P5 – Firmware           | 0 – The provided firmware is completely closed-source, and not documented at all.                                                                                                                                                                                                                                                                                                |

|                         | 1 – The provided firmware is poorly documented, possibly not completely closed-source.                                                                                                                                                                                                                                                                                           |

|                         | 2 – The interfaces are well documented, but they are not sufficiently complete to be considered straightforward to write open source software that allows the device to operate properly and fulfil its essential functions.                                                                                                                                                     |

|                         | 3 – The interfaces are sufficiently documented such that it could reasonably be considered straightforward to write open source software that allows the device to operate properly and fulfil its essential functions. The necessary software is released under an OSI-approved open source licence.                                                                            |

| P6 - Processes          | 0 – The manufacturer is not able to provide any evidence of following industry-standard best practice methodology for security-related aspects in their infrastructure, even on explicit request.                                                                                                                                                                                |

|                         | 1 – The manufacturer does not provide any formal public evidence of following industry-standard best practice methodology for security-related aspects in their infrastructures; however, they do satisfy some of the standard related requirements and are able to produce evidence on demand (e.g. they perform security testing and are able to declare to do so when asked). |

|                         | 2 – The manufacturer can provide some public evidence of following industry-<br>standard best practice methodology for security-related aspects in their<br>infrastructures; however, they do not follow a Secure Development Life Cycle<br>(SDLC) and do not possess any certification related to this topic.                                                                   |

|                         | 3 – The manufacturer can provide formal public evidence of following industry-standard best practice methodology for security-related aspects in their infrastructure, such as the implementation of a Secure Development Life Cycle, possibly with related certification (e.g. 62443-4-1).                                                                                      |

| P7 – Replicability      | 0 – The component and all of its parts can exclusively be replicated by the manufacturer, with proprietary information.                                                                                                                                                                                                                                                          |